Mart Coenen, EMCMCC, Eindhoven, the Netherlands Arthur van Roermund, Eindhoven University of Technology Mixed-signal Microelectronics, Eindhoven, the Netherlands mart.coenen@emcmcc.nl, a.h.m.v.roermund@tue.nl

Presentation outline

- Introduction

- Overview

- New approach

- Conclusions

EMC MCC ≥

#### Introduction

- With nanometre scaling, the amount of transistors/chip will follow Moore's Law.

- On- and off-chip clock and data speeds will increase further.

- Core supply voltages are reduced further down to below 1 Volt

- Peripheral supply voltages have to follow international agreed voltages levels to enable interfacing.

- While lowering the core supply voltages, the on-chip noise margin will drop accordingly

- Tight on- and off-chip decoupling measures are necessary.

- Typically, RF switching noise from digital designs are forced out of their packages through the supply and ground pins when applying conventional off-chip decoupling

#### Overview of measures

- On-chip measures

- On-chip decoupling; needed for operation

- Spread-spectrum; spreading in frequency domain

- Multi-phase clocking; spreading in time domain

- Embedded LDO; current confinement

- Variable voltage, variable frequency

- Off-chip measures

- Kelvin contacts

- Complementary off-chip measures

- Resonance free PDN design

### Overview (of what has been done)

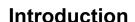

- Supply bounce; IR-drop and delay

- V<sub>ss</sub>-net/substrate analysis

EMC MCC

### EMC MCC &

### Overview (of what has been done)

Current confinement by Kelvin contacts for Off-chip decoupling

## New approach

- On-chip decoupling is always present:  $\mu\text{C}$ , DSP, FPGA, etc. both for core and peripherals

- Equivalent package induction with on-chip capacitance is at resonance below 100 MHz: example: 200 nF + 0,2 nH → ~25 MHz

- When ideally decoupled <u>off-chip</u> quality factor of resonance > 10 is reached

- Need for dampening !! (in example just 31 m $\Omega$  !!)

### **New approach**

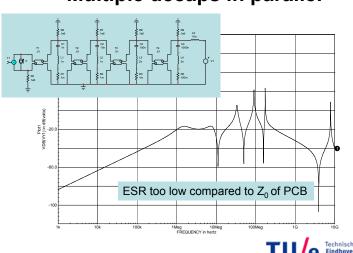

- Multiple decoupling capacitors are root cause for resonances. Values: 1:10:100:1000 are typ. placed in parallel to cover whole frequency range. ESL and physical distance add inductances thus resonances

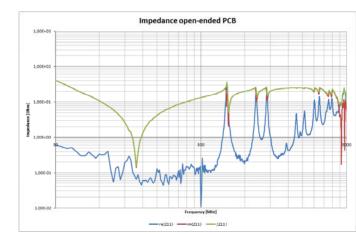

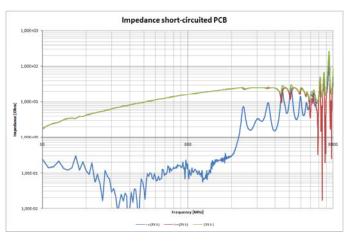

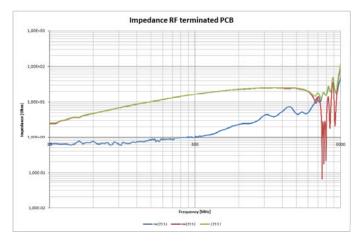

- Multiple supply/ground planes in parallel in a multilayer PCB structure are additional root cause for resonances. Open and shortcircuited TL-ends cause steep resonances from several MHz into GHz range

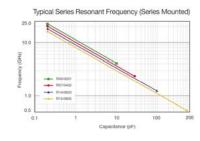

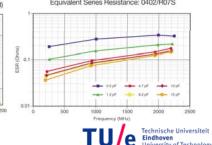

Ceramic multilayer capacitors have resonance frequency in GHz range with Q > 1000, larger capacitance → lower ESR

EMC MCC

## EMC MCC ≧√

## Multiple decaps in parallel

- Inter-plane characteristic impedance is between 0,1 and 2,5  $\Omega$ . Multiple plane pairs can be used in parallel

- Port impedance is  $Z_0/4$  as signals are propagation to all 4 edges or when rotation symmetric diverging;  $Z_0/2\pi$

- Port impedances less than 10 m $\Omega$  easy achievable; 3 plane pairs at 100  $\mu m$  spacing

# Off-center port on Euro-card, $Z_0 = 10 \text{ m}\Omega$

### New approach

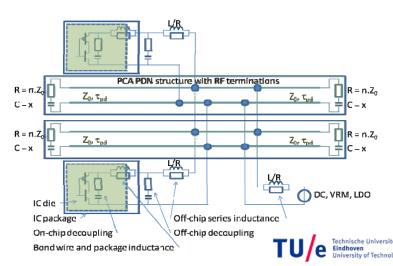

- The whole PDN chain from DC supply to the IC supply pads needs to be considered

- All "taps" and "feeds" shall:

- impedance »  $Z_0/4$  ≥  $f_{crit}$

- resonant free; Q ≤ 2

- · Due to skin and proximity effects full insulation between supply/ground currents and signal return paths are achieved skin depth = 6  $\mu$ m @ 100 MHz, Cu-layer = 37  $\mu$ m

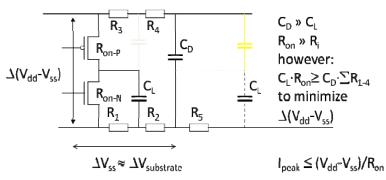

### **Total Resonant-Free PDN solution**

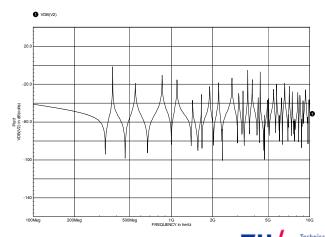

## Device port impedance Z<sub>11</sub>

# Device port impedance $Z_{11}$

## Device port impedance Z<sub>11</sub>

#### **Conclusions**

- Each part of the PDN chain shall be optimally dampened, by using: series inductance + series resistance or Kelvin contacts

- Decoupling capacitors shall be optimised for ESR too, ESL remains less critical

- Off-chip decoupling, through short PDNs, is too late for decoupling in the sub-ns region (due to self-resonance (skew) and delay of the device's PDN and in its package)

- Resonant-Free PDN is an option.